密码模块是安全保密系统的重要组成部分,其核心任务就是加/解密数据。目前,分组密码算法AES以其高效率、低开销、实现简单等特点被广泛应用于密码模块的研制。随着计算机信息技术和超大规模集成电路技术的成熟与发展,通过硬件来实现密钥模块的内部运作,可保证在外界无密钥的明文流动,能够实现真正意义上的保密。此外,硬件实现还具有高速、高可靠性等特点。目前许多AES算法的硬件实现采用基于RAM查找表方式来实现算法中最关键的SubBytes部分。本文采用复合域来实现SubBytes部分的求逆运算,以便于采用组合逻辑减小面积。同时采用加/解密运算中列变换的部分电路进行复用,从而进一步节省实现面积。这样可以使AES密码应用于RFID系统,IC卡等面积要求较小的场合。

1 AES算法简介

AES算法是一种迭代型分组密码,其分组长度和密钥长度均可变,各自可以独立指定为128 b,192 b,256 b。本文主要讨论分组长度和密钥长度为128 b的情况。AES算法是将输入的明文(或密文)分成16个字节,在第一个Add Round Keys变换后进入10轮迭代。迭代过程的前9轮完全相同,依次经过字节代替(substitute bytes)、行移位(shift rows)、列混合(mixcolumns)、轮密钥加(add round keys),最后一轮则跳过了列混合(mix columns)。解密过程与加密过程类似,但执行顺序与描述内容有所不同,因此AES算法的加解密运算需要分别实现。

2 AES算法的硬件设计

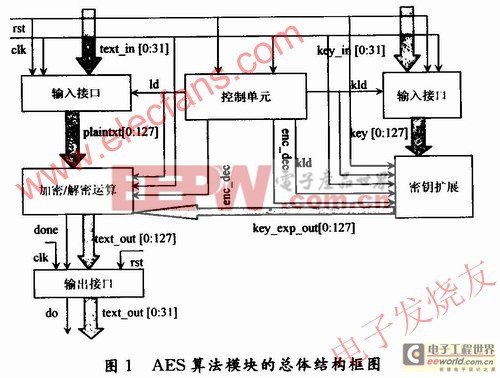

根据AES算法的原理和基本结构,将整个AES算法模块分成4个相对独立的子模块:接口模块、控制单元模块、加解密运算模块、密钥扩展模块。本文所设计的密码算法不包括密钥发生器,所用的密钥通过接口模块由外部输入,加解密运算后的数据经输出接口输出。AES算法模块的总体结构如图1所示。

2.1 接口模块的设计

输入接口模块的主要任务是:将数据传送到加解密运算模块,将外部输入的密钥传送到密钥扩展模块。由于明文和密钥输入都是128位,将导致整个模块的输入/输出过多,占用太多资源,考虑到本文的设计主要应用于对面积要求较小的场合使用,如RFID系统中数据的传输,即每次传输的数据是64位,故采用4个32位寄存器,在时钟的控制下每次输入1组32位,通过4个时钟周期可得到128位的数据,可以有效减少资源的占用。输出接口模块的作用是将128位的解密运算结果输出,同样也采取32位分4组输出的方法。

2.2 控制模块的设计

控制模块的主要任务是实现加/解密运算模块与密钥扩展模块工作的启动。控制模块在时钟脉冲控制下,产生控制加/解密模块中字节替代、行移位、列混合、密钥加各部分工作信号。可由1个两状态的状态机实现控制。当新的数据或密钥输入时,通过状态机的信号可判断上次加/解密运算是否完成。如果状态机信号处于忙状态,说明加解密运算正在进行,需要等待;如果信号处于空闲状态,说明加解密运算已经完成,可以启动加解密运算模块与密钥扩展模块,将数据和密钥分别输入到加解密运算模块与密钥扩展模块中,开始新一组数据的加解密运算。

2.3 加解密运算模块的设计

AES算法的轮变换特点使之在硬件实现时可以有多种方式:串行方式,轮变换可采用组合逻辑实现;在10轮迭代过程中,前一轮结果可直接作为下一轮的输入;并在1个周期内完成1个分组运算,使吞吐量达到最佳状态。但需要大量的存储器资源和组合逻辑资源支持,一般的FP-GA芯片难以满足容量的需求,而且时钟频率非常低;基本迭代反馈方式,所有迭代只用1个轮变换模块,10个时钟周期完成1个分组运算,资源占用较少;轮内流水线方式,在轮变换中插入寄存器,将每轮运算分成多个操作段,每个时钟完成1个操作段,其优点是可以提高算法运行的时钟频率。但轮内各级流水部件不能同时执行,因此增加了算法运行的时钟数目。轮内流水线级数越多,时钟数目也越多,虽然算法仿真频率可以达到很高,但吞吐量并没有明显提高。

综上比较可知,本文AES算法的硬件实现的目的是尽量减少资源的占用,使面积尽可能减小。故采用基本迭代反馈工作方式设计。

2.3.1 SubBytes()和InvSubBytes()的设计

字节代替是整个AES硬件实现中最为重要的变换,在加解密运算模块及密钥扩展模块中字节代替是主要的运算过程。因此,字节代替的硬件设计决定了整个AES算法硬件实现的速度和面积。字节代替可以通过查找表和算术运算的方式得到。传统的AES算法使用查找表方法实现字节代替,可以提高求逆速度,但由于该变换输入的数据为8位,加密和解密所用的替换字节表不同,因此需要的选择器和寄存器数量较多,硬件实现面积较大,故主要用于高速AES的实现。算术运算的方式在硬件设计上表现为组合逻辑,采用算术运算的方式实现则会降低硬件设计的复杂度,减小面积。

2.3.2 ShiftRows()和InvShiftRows()的设计

行移位变换作用在中间态的行上,将状态中的行按不同的偏移量进行循环移位。加密运算中间态的0~3行,分别向右循环移动O,1,2,3个字节。该操作仅是将数据按字节进行移动,硬件实现时只需在布线上进行调整,基本不占硬件资源。

解密过程只是行移位的逆变换,即分别向左循环移动0,1,2,3个字节。同样,该操作也仅将数据按字节移动。如果有字节的位置改变,只需在布线上进行修改。

2.3.3 MixColumns()和InvMixColumns()的设计

MixColumns()变换以矩阵中的列为单位,将每列看作一个GF(28)域上的四阶多项式,将多项式乘以c(x)/d(x)并对x4+1取模。其中c(x)为:

![]()

在相应的解密过程中:

![]()

同样对

![]()

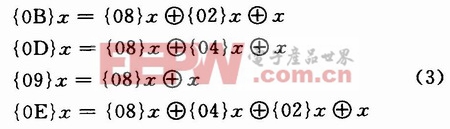

为了降低整个模块的复杂度,考虑将加解密运算中列混合变换的部分电路进行复用,对比加解密运算所乘的多项式,可以发现{03}x可以用

![]()

这样:

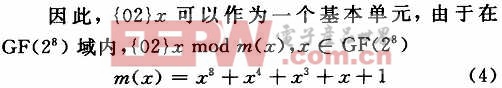

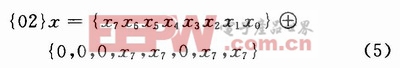

由于

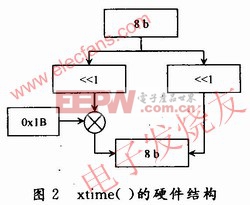

![]()

而解密时,Mixcolumns()的系数是{09,OB,OE,OD),实现这些乘法显然比加密时需要更多的时间。由式(3)可知,InvMixcolumns()也可用xtime()函数与异或门实现。这样,就可以实现加/解密列混合变换电路的复用,从而节约电路面积,提高解密运算速度。

2.3.4 密钥加AddRoundKey()的设计

在AES算法中,加法用异或操作实现。密钥加是中间状态的每一字节按位与轮密钥进行异或操作,加法的逆运算也用异或操作,所以可采用逐位异或操作实现加解密运算的AddRoundkey()。AddRoundkey()的逆运算是其自身。因此本文在常规轮中把加密时的密钥加、列混合变换和解密时的密钥加、列混合变换集成为同一模块,通过加解密信号的选择,实现加解密运算的列变换和密钥加功能。这样可消除加解密硬件结构的差异,同时也可降低轮密钥处理的复杂度。

2.4 密钥扩展模块的设计

轮密钥的产生是AES加解密运算的基础,密钥扩展模块的作用就是产生除了初始密钥本身之外的10个轮密钥,分别用于10轮加解密运算。

加密运算采用密钥内部扩展的方式,即加密运算与密钥扩展并行完成。这一过程,每一轮变换都要和相应密钥扩展轮次生成的子密钥进行异或,因此需使用状态机控制加密运算和密钥扩展的同步,否则会发生混乱。需要指出,使用内部扩展方式可以提高整个加密运算速度。而解密运算采用外部扩展方式,即密钥扩展完之后再进行解密运算,因为解密运算使用的初始密钥是密钥扩展生成的最后一轮子密钥。

3 仿真测试与结果

根据前述设计思路和优化措施,系统采用Mentor公司专门为各逻辑器件制造厂商设计的第三方专用仿真工具ModelSim 6.o进行功能仿真,给出了最后的功能仿真图。

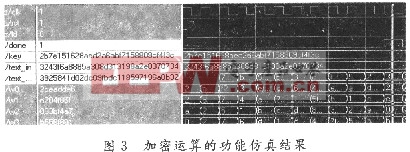

3.1 加密运算的仿真测试

一次完整的加密操作,需要12个时钟周期。其中,10个周期用于10个轮循环变换,1个时钟周期用于初始的密钥扩展,1个时钟周期用于密文的输出。加密运算的功能测试仿真波形如图3所示。

从图3给出的加密运算功能仿真结果可以看出,加密运算与密钥扩展过程是并行进行。当“rst”变为低电平,“ld”变为高电平时,明文3243f6a8885a308d313198a2e0370734与密钥2b7el5l628aed2a6abf7158809cf4f3c分别同时加载到加解密运算模块与密钥扩展模块中;在下一个时钟周期,密钥扩展模块生成1轮子密钥,等待加密轮变换中的密钥加操作。当完成1次加密过程后,“done”信号变为高电平,同时输出密文3925841d02dc09fbdc118597196a0632。从图3中同时也可以看出,密钥扩展模块总是提前一个时钟周期生成下一轮的子密钥,这样可以保证密钥扩展与加密运算同时进行而不会发生错乱,并且还可提高加密速度,节约资源占用和减少面积。使用DC进行综合和优化后,加密运算模块面积不超过20 000个等效门,其中组合逻辑面积为14 264门,非组合逻辑面积为3 878门。

3.2 解密运算的仿真测试

在解密过程中,完成一次解密操作同样需要12时钟周期。其中,10个周期用于10个轮循环变换,1个时钟周期用于初始密钥的加载,1个时钟周期用于密文的输出。在解密过程中,本文采用在解密之前所生成的10轮子密钥,因为解密初始需要的子密钥是密钥扩展得到的最后一轮子密钥,而最后一轮需要的子密钥是密钥扩展的初始密钥。如图4所示。

解密过程与密钥扩展过程不是同步的,当“kld”为高电平时,从第1个时钟周期开始,便将初始密钥2b7e151628aed2a6abf7158809cf4f-3c输入到密钥扩展模块中,之后经过10个时钟周期生成10轮子密钥,并存储到寄存器中。当“ld”为高电平时,密文3925841d02dc09fbdcll-8597196a0632开始加载到解密模块中,经过10个时钟周期将解密的密文输出,同时“done”信号变为高电平,表示解密过程结束,并输出明文3243f6a8885a308d313198a2e0370734。

对比图3与图4仿真测试结果可知,加解密运算的功能正确,即解密运算能够正确地解出加密运算的密文。解密运算模块使用DC进行综合和优化后面积不超过25 000个等效门。其中组合逻辑面积为10 495门,非组合逻辑面积为14 142门。由于密钥扩展与解密过程不是同步进行,占用了寄存器存储解密过程所需的10轮子密钥,所以非组合逻辑面积比加密运算模块大。但需要指出,由于加/解密运算模块部分电路采用复用的方法实现,所以整个加/解密运算模块的实际总面积比没有复用时减小。

4 结语

根据设计思路和优化措施,本文使用Verilog硬件描述语言实现AES密码算法,并在ModelSim 6.O工具下进行仿真,证明本文设计的正确性。为了更进一步做比较,证明本文设计思路的合理性和优化措施的有效性,同样采取未优化的设计方案实现了该算法,通过在Dc中进行综合、布线,两相比较,优化后的设计比优化前节省了22%的逻辑单元,处理速度提高了13%。